General Description

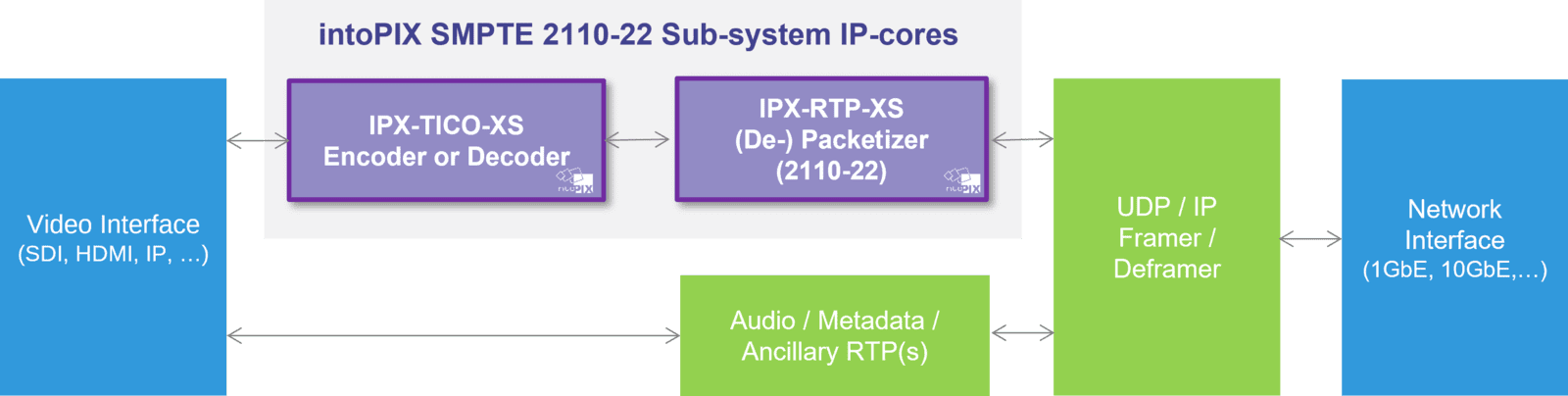

The intoPIX SMPTE 2110-22 Sub-system IP-cores (TX & RX) are combining the IPX-RTP-XS cores for JPEG XS RTP packetization / depacketization and the intoPIX JPEG XS codecs, namely the IPX-TicoXS or the IPX-TicoXS FIP IP-cores. This solution is ideal for implementers as it provides a fully integrated design, compliant with the JPEG-XS video transport over RTP standard, SMPTE 2110, IPMX, VSF TR08.

The intoPIX SMPTE 2110-22 JPEG XS RTP Sub-system IP-cores are ideal to enable any existing SMPTE ST 2110 'uncompressed' FPGA video design to rapidly support SMPTE ST 2110-22 "compressed video" , as a almost 'plug and play' solution. Moreover, it can easily integrates with 2110 cores available from third party IP providers.

Key Features

- JPEG XS RTP Payloader and Depayloader compliant with the IETF RTP Payload Format for ISO/IEC 21122 (RFC9134 / JPEG XS) and recommendations of the VSF TR08.

- Handles the complete conversion of uncompressed video to SMPTE2110-22 JPEG XS RTP packets when combined with TicoXS / TicoXS FIP encoder/decoder IP-cores

- Comprehensive software driver for codec and packetization configuration, including JPEG XS Part3 Video support Box and Colour specification boxes generation and extraction

- A SMPTE 2110-22 Sub-system IP-core that is easy to integrate with existing and third party SMPTE 2110 FPGA design (including Adeas / Nextera, Macnica)

- Full interoperable with VSF TR08 (tested by interoperability test organized by the VSF with the intoPIX ZCU106 ST2110-22 Demo)

- (Option) - Compatible with the intoPIX AES encryption IP-cores (IPX-AES) for secured RTP video transmission (such as HDCP over IP)

Note : the intoPIX Payloader and depayloader IP-core can be adapted to support other video RTP protocols willing to benefits from the full power of the JPEG XS low latency standard such as NGVA STANAG, DEF-STAN,

Video

Resources & Evaluations

Resources for Altera (Intel) or AMD (Xilinx) FPGA can be provided on request.